MS1005SK / MS1006SK

アプリケーションノート

概要/特長

近年、急速に求められている省電力化に応えるため微少負荷領域の効率を改善するウルトラスタンバイモードを備えたMS1005SK/MS1006SKを開発しました。

MS1005SK/MS1006SKは、従来に比べ待機時の入力電力を削減し様々な機能をICに内蔵することで少ない外付け部品でより使いやすく簡単に電源設計を行うことができる高機能ICです。

1. 擬似共振動作により高効率・低ノイズ化

2. 4stepソフトスタート機能内蔵

3. 起動抵抗が不要な起動回路を内蔵し、起動回路での損失を低減

4. 自動谷飛び機能により発振周波数の上昇を抑制し軽負荷時効率を改善

5. 部品追加なしに軽負荷領域の効率を改善するオートバースト(自動スタンバイ)

6. 微小負荷領域の効率を改善するウルトラスタンバイ(UT)モード

7. ノイズに有利なソフトドライブ回路を内蔵

8. 過熱保護・過電圧保護・過負荷保護(タイマーラッチ)内蔵

9. 1次電流制限回路に入力電圧依存補正回路内蔵させ部品点数を削減

10. 起動回路バイアスアシスト機能内蔵

11. Vcc-GND短絡保護機能内蔵

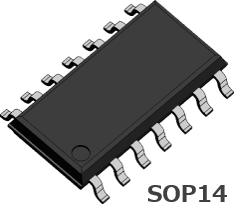

12. SOP-14パッケージを採用し、高圧ピンと制御ピン間にNCピンを3ピン確保

アプリケーションノート 目次

1 : 概要

1.1: はじめに

1.2: 特徴

1.3: 用途

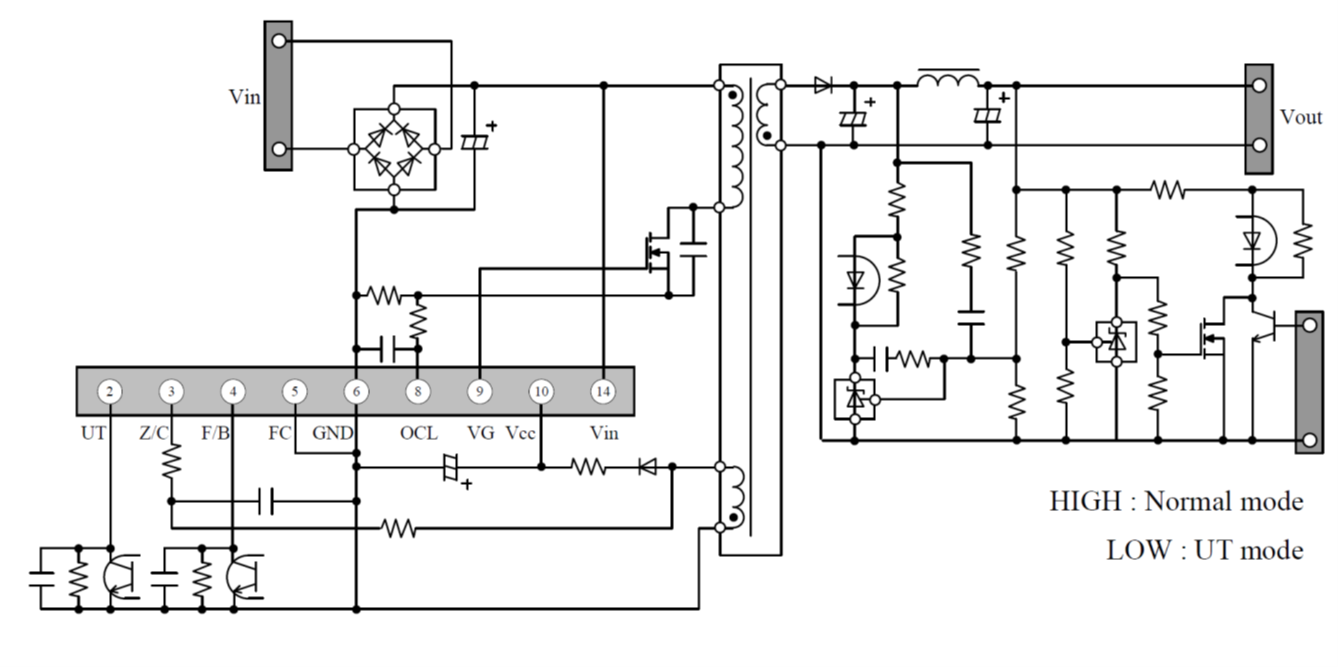

1.4: 基本構成回路

1.5: 外形寸法図

2 : ブロック図と端子名称

2.1: ブロック図

2.2: 端子名称

3 : 回路動作

3.1: 起動

3.1.1: 起動回路

3.1.2: ソフトスタート

3.1.3: バイアスアシスト

3.2: 発振動作

3.2.1: オントリガ回路

3.2.2: 擬似共振動作

3.2.3: ソフトドライブ

3.2.4: 谷飛び動作

3.2.5: 出力電圧制御

3.3: バーストモード発振動作

3.3.1: オートバースト(自動スタンバイ)

3.3.2: ウルトラスタンバイ(UV)モード

3.4: 保護機能

3.4.1: Vcc過電圧保護ラッチ(OVP)

3.4.2: 過電流保護(OCP)

3.4.3: 過負荷保護(タイマーラッチ)

3.4.4: Vcc-GND短絡保護

3.4.5: リーディングエッジブランク(LEB)

3.4.6: オントリガ誤動作防止回路(Tondead)

3.4.7: 過熱保護(TSD)

4 : 端子の機能

4.1: UT端子

4.2: Z/C端子

4.3: F/B端子

4.4: FC端子

4.5: GND端子

4.6: OCL端子

4.7: VG端子

4.8: Vcc端子

4.9: Vin端子

5 : 各端子の設計

5.1: UT端子(2番端子)

5.1.1: 標準回路

5.1.2: 部品追加によるUTモード強化

5.1.3: UTモード不使用時

5.2: Z/C端子(3番端子)

5.2.1: 標準回路

5.3: F/B端子(4番端子)

5.3.1: 標準回路

5.3.2: アブノーブル対策回路

5.3.3: F/B端子の位相補償について

5.3.4: F/B端子への付加回路について

5.4: OCL端子(8番端子)

5.4.1: 標準回路

5.4.2: 大電力時

5.5: VG端子(9番端子)

5.5.1: 標準回路

5.5.2: 駆動回路が必要な回路

5.5.3: 大電力時

5.6: Vcc端子(10番端子)

5.6.1: 標準回路

5.6.2: Vcc電圧のレギュレーション対策①

5.6.3: Vcc電圧のレギュレーション対策②

5.6.4: Vcc電圧のレギュレーション対策③

5.6.5: アブノーブル対策回路

6 : 設計方法

6.1: 設計フローチャート

6.2: メイントランス参考設計条件

6.3: メイントランス設計計算式

6.4: 各動作点を確認する

6.4.1: 式中の記号

6.4.2: 谷飛び開始電力の計算式

6.4.3: 谷飛び解除電力の計算式

6.4.4: オートバースト開始・解除計算式

6.4.5: 垂下点電力の計算式

6.5: 共振コンデンサの設定・調整

7 : UTモード使用時の2次側設計

7.1: UTモード使用時の2次側回路例

7.2: 2次側応用回路UTモードシーケンス例

7.3: 2次側応用回路の設計例

7.3.1: 出力電圧下限設定値の設定

7.3.2: Q201周辺部品の設計

7.3.3: フォトカプラPC103周辺の回路

7.4: UTモード消費電力削減例

8 : 位相補正

9 : パターン設計の注意事項

10 : ノイズ対策

回路例

| 免責事項 |

| 当ウェブサイトから本資料をダウンロードされる前に以下の免責事項を十分にお読みいただき、同意される場合にのみ同意ボタンからダウンロードを行なって下さい。 |

|